|

Model |

RA8L |

RA8 |

|

Core |

Application Core: Cortex-M7; Secure Core: Cortex-M0 |

|

|

Core Qty. |

2 (Lockstep) + 1 |

|

|

Flash |

2MB |

4MB |

|

SRAM |

256KB |

512KB |

|

Secure RAM |

64KB |

64KB |

|

DSP |

Yes |

|

|

FPU |

Double Precision |

|

|

Embedded HSM |

EVITA Full ECC、SHA、SM2/3/4… |

|

|

CAN-FD |

Up to 8 |

Up to 8 |

|

LIN |

4 |

4 |

|

Ethernet |

100M/1000M TSN |

100M/1000M TSN |

|

SPI |

6 |

6 |

|

QSPI |

2 |

2 |

|

UART |

4 |

4 |

|

DMA |

32 |

32 |

|

ADC |

48 |

48 |

|

SENT |

6 |

6 |

|

I2C |

2 |

2 |

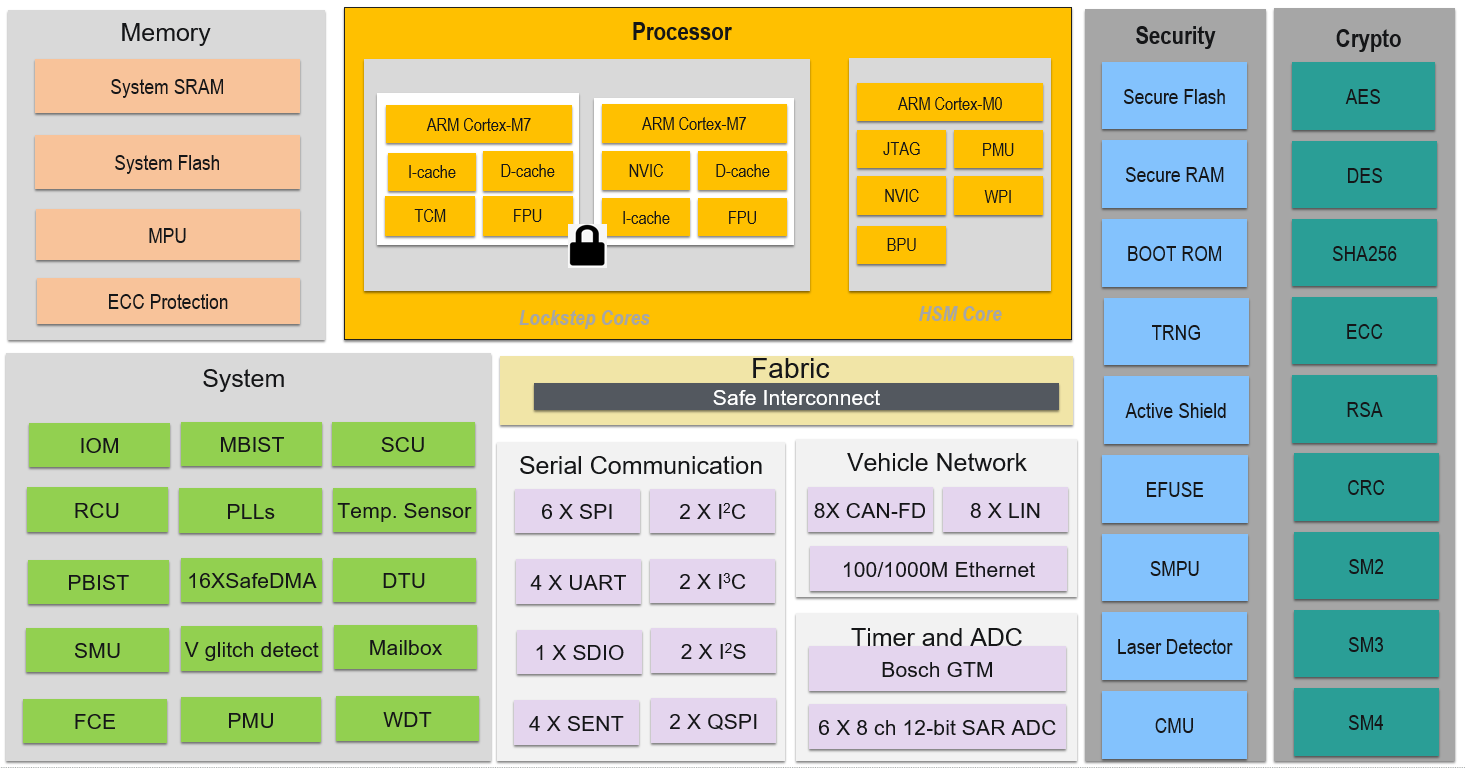

RA8 Block Diagram

features

• system

- Power supply: 5V, 3.3V and 1.2V at the same time;

- Application kernel: a set of Cortex-M7 dual-core lockstep, main frequency up to 240MHz, up to 600 Dhrystone MIPS;

- Security kernel: a cortex-M0 kernel, 48MHz;

- Interrupt controller: two sets of NVIC;

- Hardware single increment counter: supports 64-bit system counter

- DMA controller: 32 safe DMA channels;

- Debugging control: the application system supports ARM CoreSight JTAG debugging and Trace debugging; Information security system does not support any debugging, only support internal configuration and call;

- Power mode: support normal operation, low power mode, sleep mode and other power modes;

-Operating temperature: -40-125 °C;

- IO level: supports 5V IO and 3.3V IO.

• memory

- system Flash: up to 4MB ECC;

- System RAM: up to 512KB ECC;

- security Flash: 512KB ECC;

- Secure RAM: 64KB ECC;

- QSPI: a single QSPI supports a maximum of 256 MB external storage.

• communication

- CAN: supports up to 8 channel CAN-FD, compatible with CAN 2.0B;

-LIN: supports a maximum of eight channels.

- Ethernet: 1000 MBIT/s TSN Ethernet supports MII, RMII, and GMII interfaces. 100M Ethernet supports RGMII interface.

- UART: supports a maximum of 4 channels and a baud rate of 5 Mbit/s.

- QSPI: supports a maximum of two groups. Each group supports one input and two outputs. The baud rate is up to 10 Mbit/s.

-spi: supports a maximum of 6 channels and a baud rate of up to 10Mbps.

- SENT: supports a maximum of six routes.

- I2C: supports a maximum of two groups.

- I2S: supports a maximum of two groups.

- SDIO: supports a maximum of 1 group.

- I3C: supports a maximum of 2 groups;

• simulation

- Supports up to 6 sets of 48 12-bit successive approximation adCs;

• the timer

- GTM GEN4.1: 32-bit universal timer, supports up to 32 channel TIM, 32 channel TOM, 64 channel TIO and 24 channel MCS;

- FTM: 16-bit flexible timer, supports up to 8 groups of 64 channels, supports input capture, output comparison and orthogonal codec functions;

The clock,

- FIRC: internal high speed clock frequency 48MHz;

- SIRC: internal low speed clock frequency 32kHz;

- FXOSC: external input clock frequency 40MHz;

• Functional safety

-IO monitor;

-Security DMA;

- Reset control unit;

- Safety management unit;

- Failure control engine;

- Window type watchdog;

- Temperature failure detection;

- Overvoltage and undervoltage detection;

• certification

- ISO 26262 ASIL-D

- OSCCA Certification Grade 2

- EAL4+

- AEC-Q100 Certification Grade1

• packaging

- BGA-180

- LQFP-100

• Information security

- Support high-speed ECDSA (NIST-P256);

- SM2;

- SM3;

- RSA (a maximum of 2048 bits).

ECC - 256;

- SHA - 256;

- AES;

- DES;

- SM4;